click image to enlarge

Overview

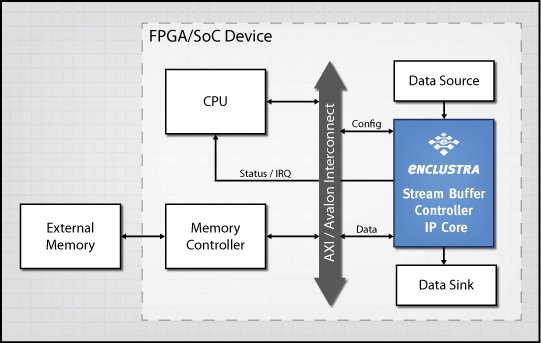

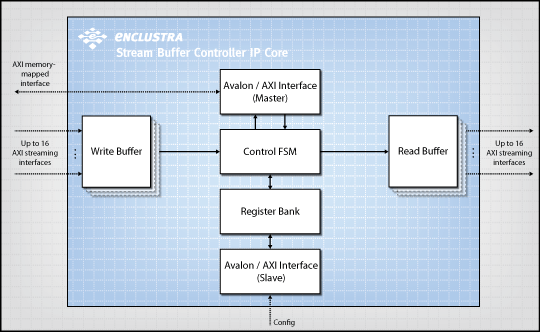

The Stream Buffer Controller IP Core is optimized for Intel (Altera) and Xilinx FPGAs and implements a versatile Stream to Memory Mapped DMA bridge with 16 independent streams. The IP core allows data buffering in an external memory device to provide virtual FIFO capability with up to 4 GB memory size. It provides AMBA® AXI4-Stream interfaces for each write and read data stream. A common memory-mapped master interface (AXI or Avalon) is provided to access the external memory device over an interconnect.

The IP core is highly configurable in terms of operation mode, buffer size and buffer address for each stream. The configuration is done over a memory mapped slave interface, either by an embedded-CPU, by a FPGA Manager application or by an application specific stream configurator controller in VHDL.

Highlights

- The IP Core supports four different operation modes for each channel:

- FIFO mode: writing and reading to the memory is done over the AXI4-Stream interfaces

- Write mode: Writing to the memory is done over the AXI4-Stream, Reading from the memory is done by a CPU.

- Read mode: Writing to the memory is done by a CPU, reading from the memory is done over the AXI4-Stream interface.

- ROM mode: Reading from the memory is done over the AXI4-Stream interface. The memory must be initially written by a CPU

Benefits

- Supports data width conversion for the write and read data streams

- The use of different operation modes provides the implementation of versatile applications with a single IP core.

- Easy integration thanks to the unified bus interface and the clearly laid out register bank

- A stand-alone solution without the need of a CPU can be easily realized by a stream configuration controller that is provided in VHDL

Features

- Supports up to 16 write and read streams (depending on product options)

- Configurable status flags for write and read path

- Vendor-independent implementation

- Available with Avalon or AMBA-AXI interface

- Data width conversion to/from any byte-multiple width

Architecture

click image to enlarge

Product Selection Matrix

| Product Code | Description |

|---|---|

| EN-SBC-BASE1 | Base license, 2 channels |

| EN-SBC-OPT-XIL | Xilinx FPGA support |

| EN-SBC-OPT-ALT | Intel FPGA support |

| EN-SBC-OPT-ADV | Advanced features: 16 channels, multi-width and more |

1: The base package requires at least one of the Xilinx/Intel as well as one output option. 2: Only available for Xilinx.

Deliverables

- Stream Buffer Controller IP Core

- VHDL source files (plain or encrypted, depending on product options)

- Reference design

- User manual

- Stream Buffer Controller API

- C source code

- Application software example

- User manual

- Stream Buffer Controller IP core reference design

- Reference design top-level VHDL file (plain VHDL)

- UCF / XDC / SDC constraint files (depending on product options)

- Xilinx® ISE / Xilinx Vivado™ / Intel® Quartus® project files (depending on product options)

- Top-level simulation test bench file (plain VHDL)

- Top-level simulation ModelSim project file

- Documentation

Site Licence Model

- The license is granted to an “authorized site”, meaning a single geographical location with radius < 5 km in which the licensee conducts business.

- The licensed material can be used for unlimited projects and/or end products developed at the authorized site.

Target Applications

- Embedded Computing

- Data Acquisition

- High-Speed Communications

- Drive/Motion Control

- Digital Signal Processing

- Image Processing

Related Products

- FMC DR2 Drive Control Card

Information on the product may change, please check the manufacturers website and page for the most up to date information, see the link at the top right of this page.