click image to enlarge

Overview

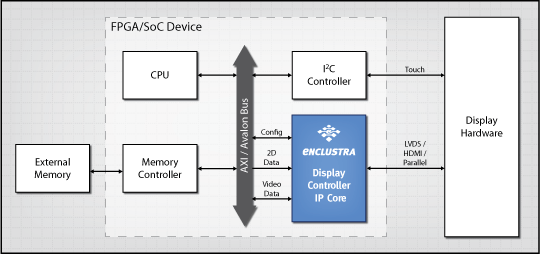

The Display Controller IP Core is optimized for Intel (Altera) and Xilinx FPGAs and enables the easy addition of a display to existing or future FPGA designs, allowing the system designer to focus on the main application instead of dealing with display control issues. In addition, there is no need for an external display controller device that would consume precious PCB space and unnecessarily extend the project’s BOM.

With its modular design and strong scalability, the Display Controller IP Core perfectly fits the system requirements without wasting any FPGA resources. These unique features will also simplify the reuse of the Display Controller IP Core in future projects. Selecting our Display Controller IP Core for the display control needs of present or future projects will significantly reduce time to market as well as the overall system cost.

Highlights

- Support for parallel, LVDS and HDMI/DVI displays without external display controller device

- Support for unlimited video pages

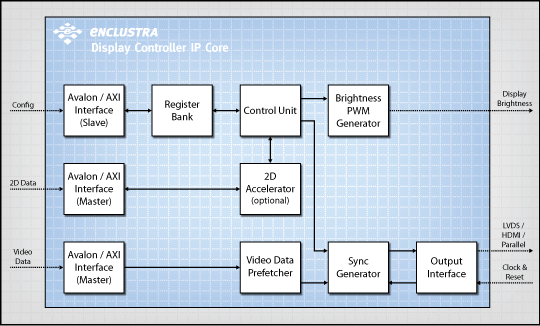

- Built-in PWM generator for display brightness control

- Optional 2D accelerator unit (draw/copy rectangles, supports transparent color)

- AXI/Avalon bus interface for both register bank and frame buffer memory access

- Linux driver

Benefits

- No need for an external display controller device which results in a smaller PCB and a reduced BOM

- Low resource usage and good scaling due to modular design

- Easy integration thanks to the unified bus interface and the clearly laid out register bank

Features

- Supported color modes:

-

- 16-bit true color (5/6/5)

- 24-bit true color

- Supported display resolutions:

-

- Up to 1280 × 1024 on low-cost FPGAs*

- Up to 1920 × 1080 on high-performance FPGAs1

- 1Note that these resolutions are for reference only and thus not guaranteed; the maxium achievable resolution is dependent on system design factors like memory bandwidth, clock frequency, etc.

Architecture

click image to enlarge

Product Selection Matrix

| Product Code | Description |

|---|---|

| EN-DISP-BASE1 | Base license, 2 channels |

| EN-DISP-OPT-XIL | Xilinx FPGA support |

| EN-DISP-OPT-ALT | Intel FPGA support |

| EN-DISP-OPT-CMOS | Parallel output support |

| EN-DISP-OPT-LVDS | LVDS display support |

| EN-DISP-OPT-HDMI2 | DVI/HDMI output support |

| EN-DISP-OPT-CL | Camera link support |

1: The base package requires at least one of the Xilinx/Intel as well as one output option. 2: Only available for Xilinx.

Deliverables

- Display Controller IP Core

- VHDL source files (plain or encrypted, depending on product options)

- Reference design

- User manual

- Display Controller IP Core reference design

- Reference design top-level VHDL file (plain VHDL)

- UCF / XDC / SDC constraint files (depending on product options)

- Xilinx® ISE / Xilinx Vivado™ / Intel® Quartus® project files (depending on product options)

- Top-level simulation test bench file (plain VHDL)

- Top-level simulation ModelSim project file

- Documentation

Site Licence Model

- The license is granted to an “authorized site”, meaning a single geographical location with radius < 5 km in which the licensee conducts business.

- The licensed material can be used for unlimited projects and/or end products developed at the authorized site.

Target Applications

- Embedded Computing

- Data Acquisition

- High-Speed Communications

- Drive/Motion Control

- Digital Signal Processing

- Image Processing

Information on the product may change, please check the manufacturers website and page for the most up to date information, see the link at the top right of this page.