Overview

The Mars XU3 system-on-chip (SoC) module combines Xilinx’s Zynq UltraScale+ MPSoC device with fast DDR4 SDRAM, eMMC flash, quad SPI flash and a Gigabit Ethernet PHY, USB 3.0 and thus forms a complete and powerful embedded processing system.

The SO-DIMM form factor allows space-saving hardware designs as well as quick and simple integration of the module into the target application.

The Mars XU3 SoC module reduces development effort, redesign risk and improves time-to-market for your embedded system.

Highlights

- Built around Xilinx’s Zynq UltraScale+ MPSoC

- Combines the flexibility of a CPU system with the parallel processing power and real-time capabilities of an FPGA system

- Fast DDR4 SDRAM

- Supports analog differential inputs

- Available in industrial temperature range

- Supports USB 3.0, CAN, Gigabit Ethernet and PCIe® Gen2 x4

- Linux BSP and tool chain available

Benefits

- A complete and powerful embedded processing system in the industry-standard SO-DIMM form factor

- Simple, low cost and yet rugged assembly

- Simple and low-cost integration due to the on-board standard interfaces (USB, Ethernet, CAN)

- High-bandwidth program and data memory due to the high-performance hard-macro memory controller

- Lowest power consumption due to the high-efficiency DC/DC converters

Features

- Xilinx® Zynq Ultrascale+™ MPSoC

- ARM® quad-/dual-core Cortex™-A53

(64 bit, up to 1333 MHz) - ARM dual-core Cortex™-R5

(32 bit, up to 533 MHz) - 16nm FinFET+ FPGA fabric

- ARM® quad-/dual-core Cortex™-A53

- Mali-400MP2 GPU

(only EG variants) - Up to 4 GB DDR4 SDRAM

- 64 MB QSPI flash

- 16 GB eMMC flash

- Gigabit Ethernet

- USB 3.0

- USB 2.0 OTG.0

- PCIe® Gen2 ×4

- 4 × 5 Gbit/sec MGT

- Up to 154,000 LUT4-eq

- 108 user I/Os

- 12 ARM peripherals

- 76 FPGA I/Os

- 20 MGT signals (clock and data)

- 67.6 × 30 mm SO-DIMM

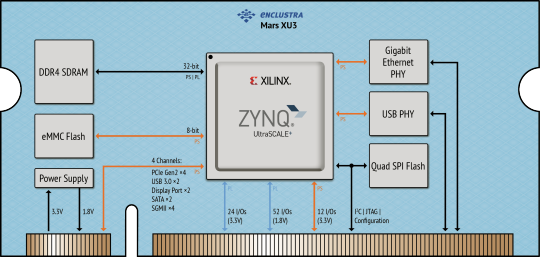

Module Architecture

Click image to enlarge

Not all features are available simultaneously – please check the documentation for any applicable constraints.

All specifications are subject to change without notice. Please verify component specifications with vendor’s datasheets.

Enclustra maintains an errata and revision history document for each product. Please also check the errata of the FPGA device and other components.

Product Selection Matrix

| Product Code |

|

|

|

|

|---|---|---|---|---|

| MA-XU3-2CG-1E-D10 | XCZU2CG-1SBVA484E | 1GB | 0 to +85°C | |

| MA-XU3-2EG-1I-D10 | XCZU2EG-1SBVA484I | 1GB | -40 to +85C | |

| MA-XU3-3EG-2I-D11 | XCZU3EG-2SBVA484I | 2GB | -40 to +85C |

Key: ![]() Mass Production

Mass Production ![]() Sampling

Sampling ![]() Contact us

Contact us

Mars Heatsink

The Mars heat sink is an optimal solution to cool the Mars XU3 – it’s low profile (less than 7 mm tall) and covers the whole module surface. It comes with a gap pad for the FPGA and four screws to attach it to the module PCB. With additional user configured gap pads, it is possible to cool other components on board as well.

To cool the module even further, a mounting slot in the center of the heat sink makes it easy to attach fans of different sizes – see the technical drawing for details.

Base Boards

| Base Board | Description |

|---|---|

| Mars ST3 | An ideal platform for display applications |

| Mars EB1 | An ideal platform for a stereo frame grabber and other video applications. |

Operating System Support

OS | Details | Availability | Partner |

|---|---|---|---|

Linux | BSP support for: DDR4 SDRAM eMMC flash Quad SPI flash USB host Gigabit Ethernet U-boot bootloader Comprehensive user documentation Software development how-to guide. | Available Now |

Target Applications

- Embedded Computing

- Data Acquisition

- High-Speed Communications

- Drive/Motion Control

- Digital Signal Processing

- Image Processing

Related Products

- Mars ST3 Base Board

- Display Controller IP Core

- Mars EB1 Base Board

- Advanced Velocity Estimator IP Core

Information on the product may change, please check the manufacturers website and page for the most up to date information, see the link at the top right of this page.