Universal Drive Controller IP Core

click image to enlarge

Overview

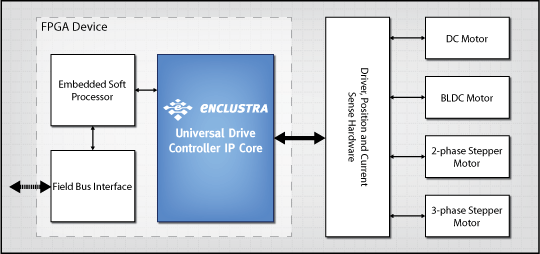

The Enclustra Universal Drive Controller IP Core is optimized for Intel (Altera) and Xilinx FPGAs and enables the easy addition of drive control capabilities to existing or future FPGA designs. There is no need for an extra drive controller chip that would consume precious PCB space and unnecessarily extend the project BOM.

Selecting Enclustra’s Universal Drive Controller IP Core for the drive control needs of future projects will significantly reduce time to market as well as the overall system cost.

Highlights

- Evaluation Kit available

- Support for DC, BLDC and 2-phase stepper motors

- Support for encoders and resolvers

- Field oriented control (FOC) for BLDC motors

- Completely autonomous error handling

- Optimized for lowest total

solution cost - Support for ADC-sharing between different devices

Benefits

- Significantly lower CPU load due to completely autonomous control loops

- Single-chip solution (fieldbus access, CPU and drive controller on the same chip)

- Easy integration, lowest solution cost

- Plenty of parallel processing power, zero jitter

- Well defined interfaces for customization

- Great reusability due to configurable controller structure

Features

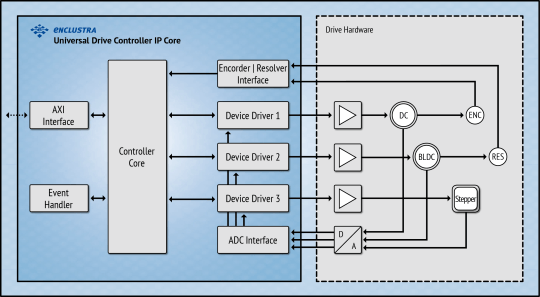

- Up to 8 drives per controller

- Up to 4 PID controllers per drive (position, velocity, current(s)) at up to 200kHz control rate

- Velocity- and acceleration-feed-forward

- Voltage, current and temperature supervision

- Separate PWM clock domain for high-resolution PWM

- Vendor-independent implementation

- Industry Standard AXI-4 interface

- Fully integrated with vendor tools (Quartus/QSYS, Vivado/IPI)

Architecture

click image to enlarge

Evaluation Kit

click image to enlarge

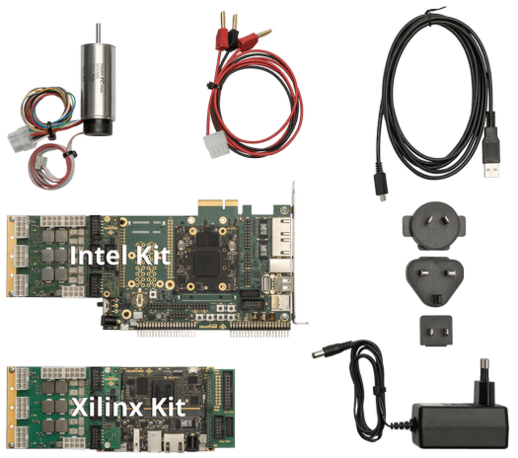

The Universal Drive Controller Evaluation Kit provides a full featured design platform to build motion control applications. The kit provides an out-of-the box hardware platform with reference design, to reduce development time and allow you to focus on your target application. The kit is comprised of1:

- Universal Drive Controller IP Core, Evaluation License

- Supports up to 2 DC, stepper or BLCD motors

- Encrypted VHDL

- 1-hour time bomb

- Evaluation platform, containing:

- Xilinx: Mars ZX3 SoC module (MA-ZX3-20-1C-D9) & Mars PM3 base board or

- Intel: Mercury SA1 SoC module (ME-SA1-C6-7I-D10) & Mercury+ PE1-200 base board

- FMC-DR2 FMC drive control card

- An appropriate motor:

- Maxon BLDC motor (EC-max 30 with MR encoder, 24 V Version) or

- a DC motor or

- a stepper motor

- Reference design

- Two hours of included support2

1: 24V DC power supply required. Functional testing of the FMC-DR2 card is limited to the Drive Evaluation Kit.

2: Included only once per site and year

Product Selection Matrix

| Product Code | Description |

|---|---|

| EN-DRV-BASE* | Base license, 2 channels |

| EN-DRV-OPT-XIL | Xilinx FPGA support |

| EN-DRV-OPT-ALT | Intel FPGA support |

| EN-DRV-OPT-DC | DC device unit |

| EN-DRV-OPT-BLDC | Brushless DC device unit |

| EN-DRV-OPT-SM2 | 2-phase stepper motor device unit |

| EN-DRV-OPT-CH8 | 8 channel support |

| EN-DRV-OPT-RES | Resolver interface |

| EN-DRV-OPT-MADC | Multi-ADC interface (AD7266) |

*The base package requires at least one of the Xilinx/Intel as well as one device unit options.

Deliverables

- Universal Drive IP Core

- VHDL source files (plain or encrypted, depending on product options)

- Reference design

- User manual

- Universal Drive API

- C source code

- Application software example

- User manual

Site Licence Model

- The license is granted to an “authorized site”, meaning a single geographical location with radius < 5 km in which the licensee conducts business.

- The licensed material can be used for unlimited projects and/or end products developed at the authorized site.

Target Applications

- Embedded Computing

- Data Acquisition

- High-Speed Communications

- Drive/Motion Control

- Digital Signal Processing

- Image Processing

Related Products

- FMC DR2 Drive Control Card

Information on the product may change, please check the manufacturers website and page for the most up to date information, see the link at the top right of this page.